Propuesta de interfaz QL-IDE para puerto de cartucho ROM

Publicado: Mié Jul 21, 2010 6:23 am

Esto viene oriignalmente del hilo en el que se habla sobre la Minerva y la MKII en una única ROM.

De momento, esto es sólo una propuesta que he hecho esta noche, "a ver cómo sale". Todo el diseño se basa en la premisa (que tendría que comprobar) de que ROMOEH se activa tanto para accesos de lectura al área de la ROM como en accesos a escritura (aunque en una ROM esto no tenga sentido, claro).

Resulta una placa que mediría 64mm de ancho X 92mm de largo (incluyendo el conector de borde que se enchufa al QL). La parte que sobresale del QL son unos 74mm.

En el conector IDC40 se puede pinchar un disco duro, o bien un adaptador IDE-CF, o un adaptador IDE-SD. Dado que los primeros son unos adaptadores muy muy baratos, no merece la pena integrar el conector de CF en el diseño. Claro que esto tiene el inconveniente de que sobresale por arriba, y bueno, quizás no queda muy estético. A mi la verdad es que el tema estético me da bastante lo mismo.

Se usa el dispositivo IDE en toda su capacidad, esto es, con la interfaz de 16 bits, si bien a causa del formato usado, todas las lecturas y escrituras deberán hacerse de 8 en 8 bits.

Un LED indica cuándo hay actividad en el dispositivo que enchufemos (disco duro, CF, etc).

Una ROM de 16K contendrá el firmware. De estos 16K, los últimos bytes (de momento, los últimos 16, es decir, el rango FFF0-FFFF) no direcciona realmente la ROM sino la interfaz IDE. Como no tenemos señal de escritura, el truco (que también se usa en los dispositivos que se implementan en forma de cartucho ROM del Inteface II) consiste en reservar un rango de direcciones para acceder al dispositivo en lectura, y otro rango distinto para acceder a él en escritura. Así, el registro de datos estaría en la posición FFF0, y si queremos leer un byte de él, leeríamos esa dirección, pero si queremos escribir un byte a ese registro, no escribiremos en esa dirección sino que lo haremos en FFF8.

Dicho de otra forma: la línea de dirección A3 hace el papel de señal de lectura/escritura: si A3 vale 0, estamos leyendo. Si vale 1, estamos escribiendo. Pero este rol sólo es válido si el rango que se direcciona es el resrvado para la interfaz IDE.

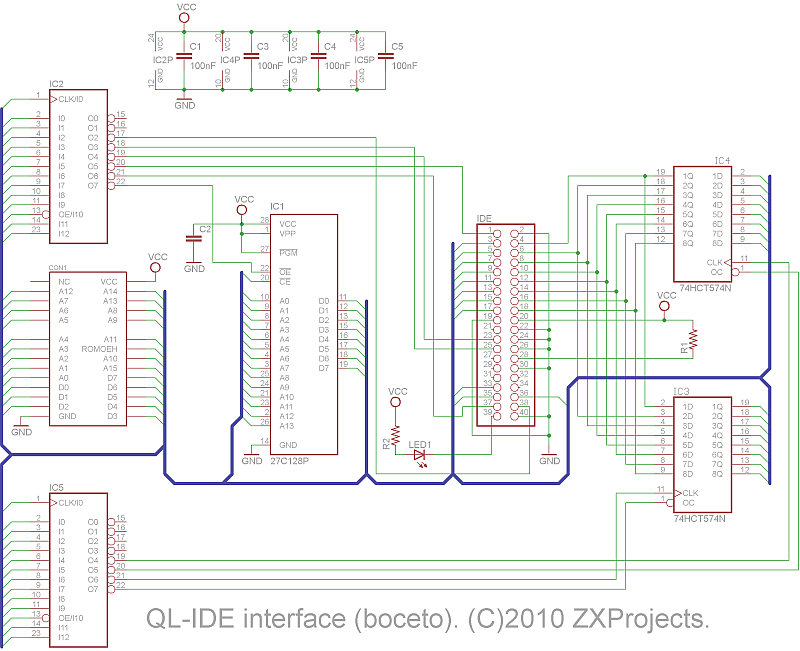

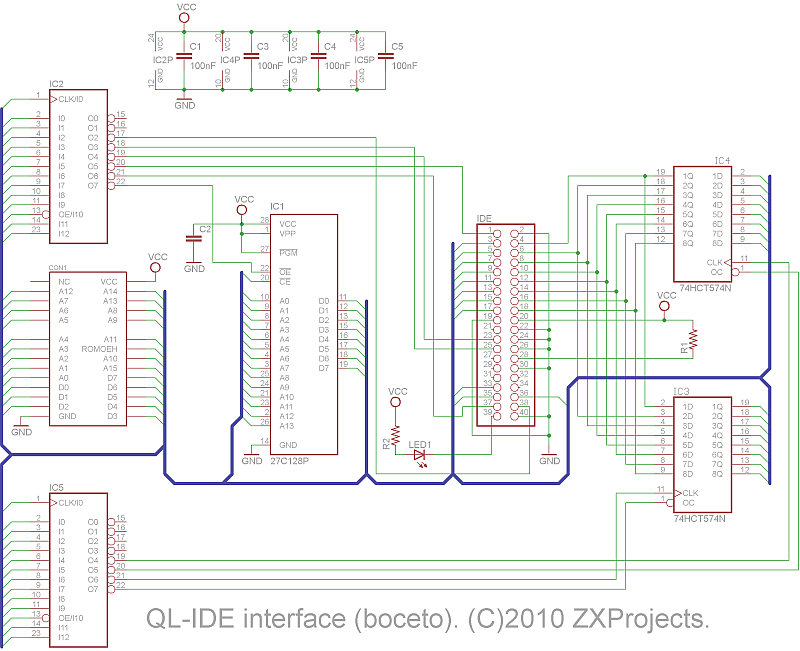

Esquemático (muy muy simple, y por tanto, sujeto a múltiples errores)

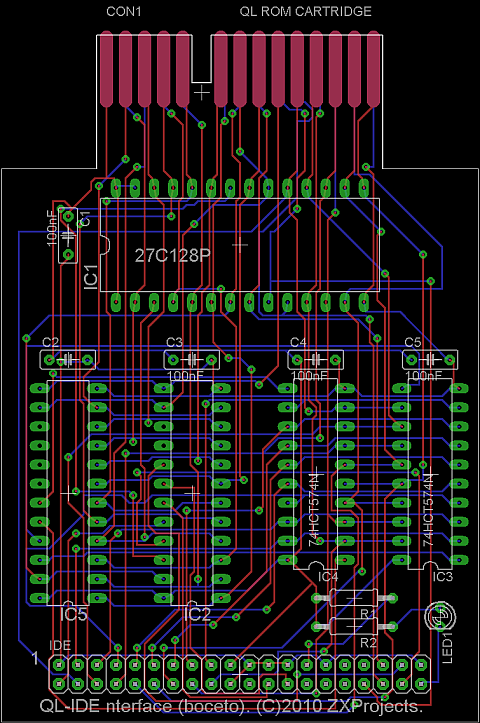

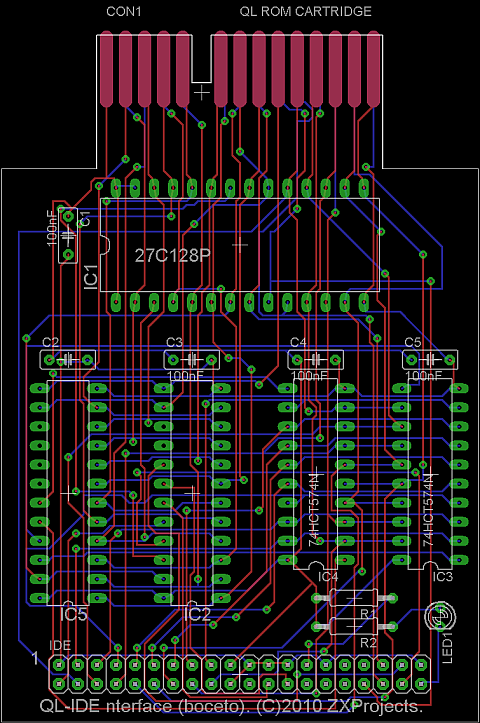

PCB:

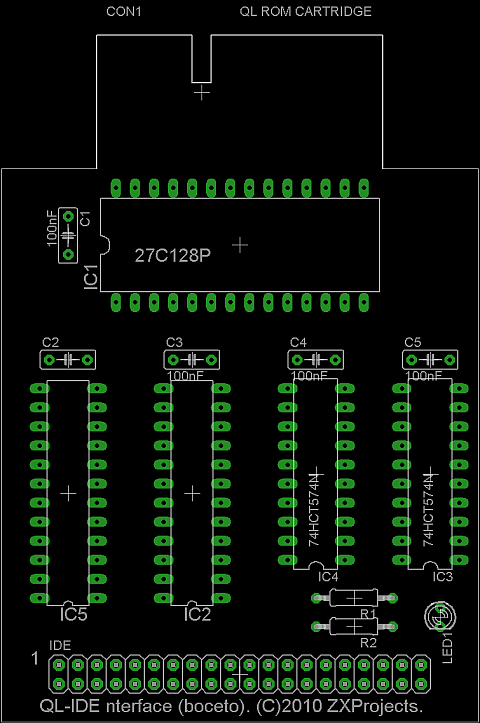

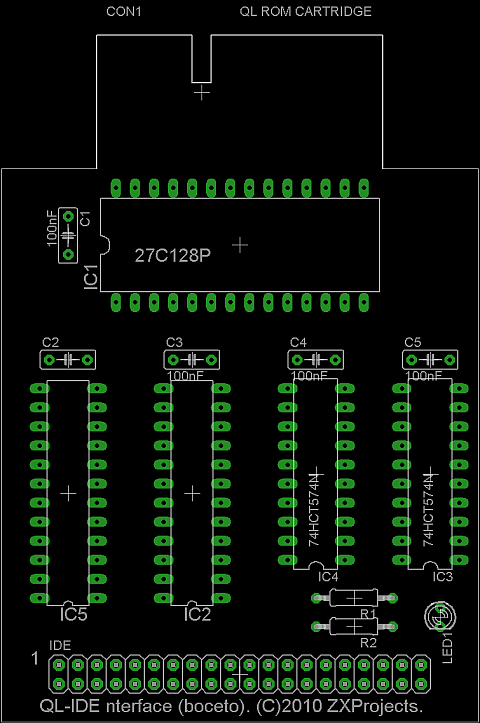

Disposición de los componentes en la placa:

De momento, esto es sólo una propuesta que he hecho esta noche, "a ver cómo sale". Todo el diseño se basa en la premisa (que tendría que comprobar) de que ROMOEH se activa tanto para accesos de lectura al área de la ROM como en accesos a escritura (aunque en una ROM esto no tenga sentido, claro).

Resulta una placa que mediría 64mm de ancho X 92mm de largo (incluyendo el conector de borde que se enchufa al QL). La parte que sobresale del QL son unos 74mm.

En el conector IDC40 se puede pinchar un disco duro, o bien un adaptador IDE-CF, o un adaptador IDE-SD. Dado que los primeros son unos adaptadores muy muy baratos, no merece la pena integrar el conector de CF en el diseño. Claro que esto tiene el inconveniente de que sobresale por arriba, y bueno, quizás no queda muy estético. A mi la verdad es que el tema estético me da bastante lo mismo.

Se usa el dispositivo IDE en toda su capacidad, esto es, con la interfaz de 16 bits, si bien a causa del formato usado, todas las lecturas y escrituras deberán hacerse de 8 en 8 bits.

Un LED indica cuándo hay actividad en el dispositivo que enchufemos (disco duro, CF, etc).

Una ROM de 16K contendrá el firmware. De estos 16K, los últimos bytes (de momento, los últimos 16, es decir, el rango FFF0-FFFF) no direcciona realmente la ROM sino la interfaz IDE. Como no tenemos señal de escritura, el truco (que también se usa en los dispositivos que se implementan en forma de cartucho ROM del Inteface II) consiste en reservar un rango de direcciones para acceder al dispositivo en lectura, y otro rango distinto para acceder a él en escritura. Así, el registro de datos estaría en la posición FFF0, y si queremos leer un byte de él, leeríamos esa dirección, pero si queremos escribir un byte a ese registro, no escribiremos en esa dirección sino que lo haremos en FFF8.

Dicho de otra forma: la línea de dirección A3 hace el papel de señal de lectura/escritura: si A3 vale 0, estamos leyendo. Si vale 1, estamos escribiendo. Pero este rol sólo es válido si el rango que se direcciona es el resrvado para la interfaz IDE.

Esquemático (muy muy simple, y por tanto, sujeto a múltiples errores)

PCB:

Disposición de los componentes en la placa: