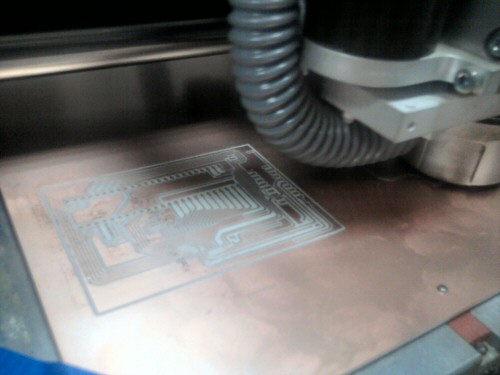

Vale, pues esto ya funciona. Unas fotillos, mientras explico cómo ha ido la cosa:

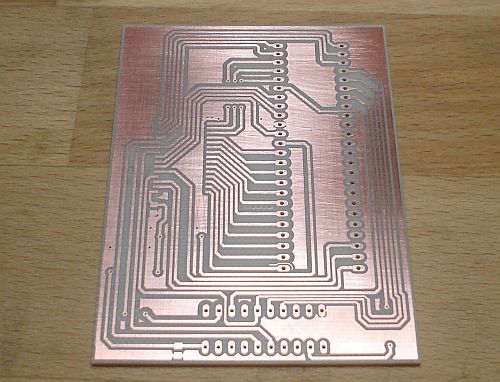

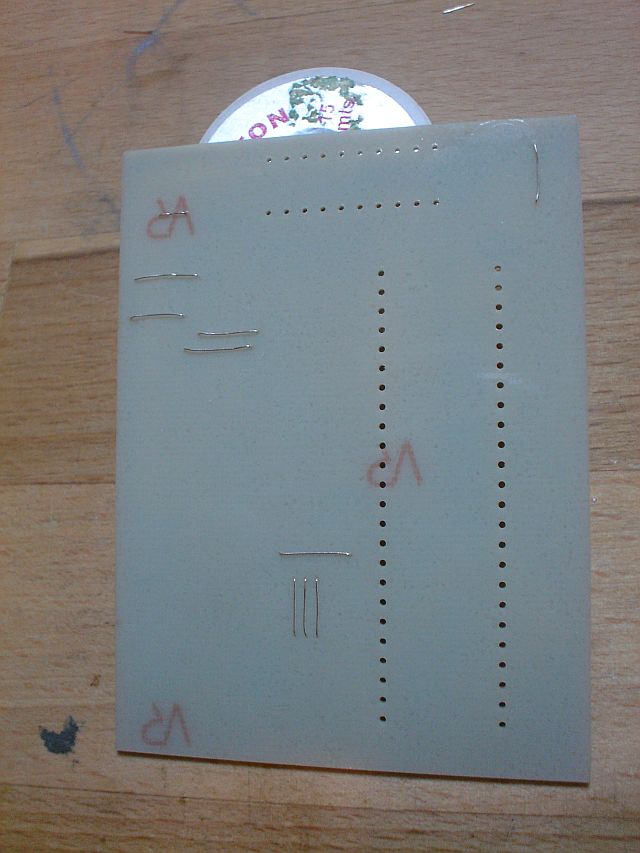

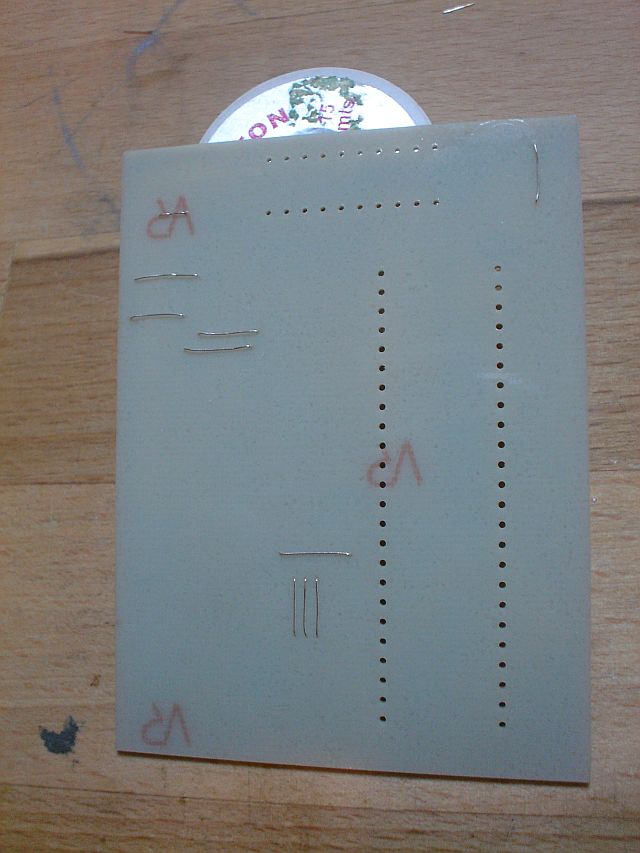

La placa, con los puentes soldados (las pistas en rojo en la PCB, para no tener que usar una placa de doble cara):

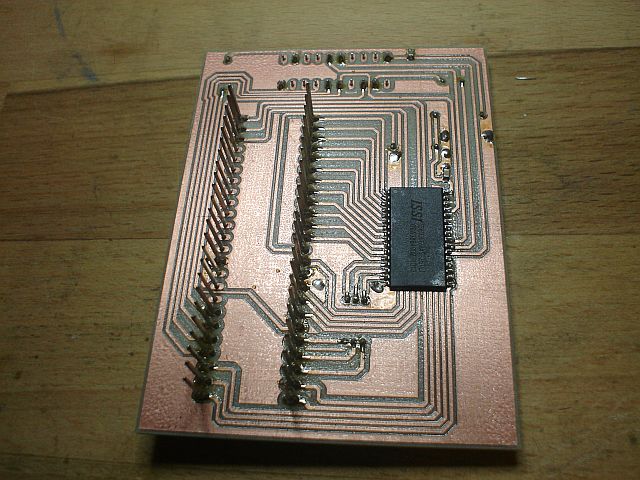

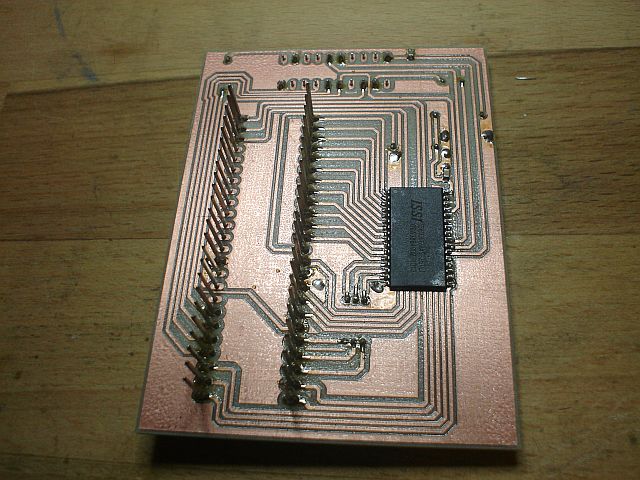

Una vez puestos los puentes, soldamos los componentes SMD: dos pequeños condensadores de desacoplo (casi no se verán en la foto), y la memoria. Soldar la memoria es más sencillo de lo que parece: se "presenta" el chip a la placa, se embadurna de flux las dos filas de pines, se pone un pegote de estaño en la punta del soldador, y se "pasea" la punta por tooooda la fila. Si se formaran puentes juntando dos o más pines, se limpia con la malla desoldadora.

Después de la memoria se suelda el zócalo para la GAL, y el zócalo de patas largas para el 68008 (en realidad son dos zócalos de 24 pines unidos, de los que se usan para diseño wire-wrapping)

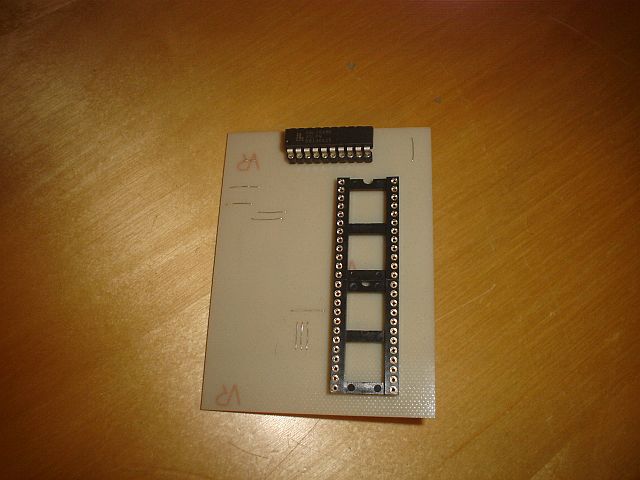

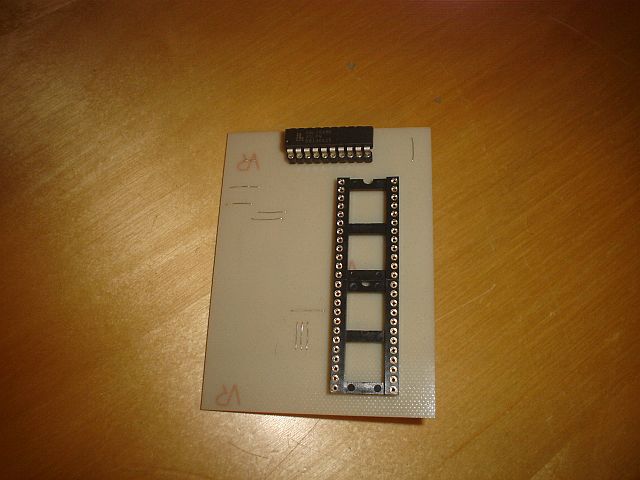

La cara de componentes sólo tiene los zócalos para los chips. Aquí está ya puesta la GAL.

La placa, ya pinchada sobre el zócalo del 68008. Por supuesto, el QL no se puede cerrar con esta placa puesta, pero me da igual, ya que sólo quiero cercionarme de que esto funciona. Ya he comentado en posts anteriores que debido a esto, y a que cierta señal que me hace falta está sólamente disponible en el conector de expansión, esta ampliación, para ser usada "en producción" debería ir pinchada a dicho conector.

El cablecillo que sale de la GAL hacia la placa ha sido el quebradero de cabeza de estas últimas 24 horas.

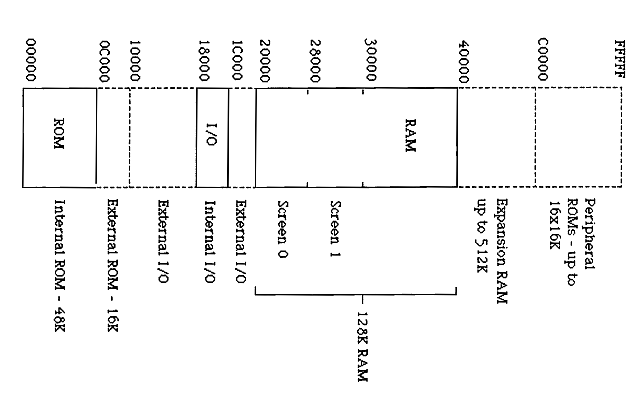

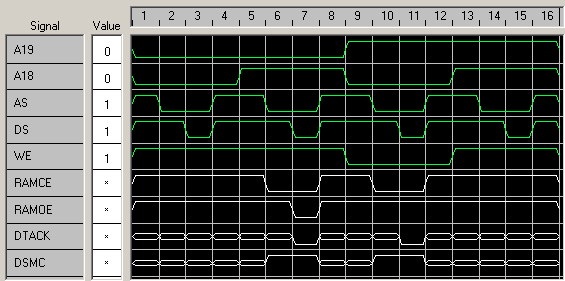

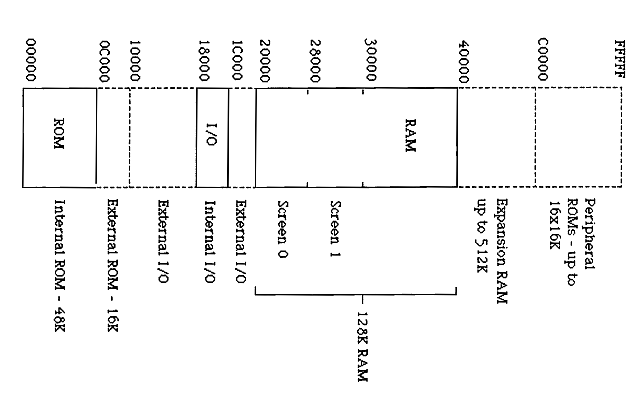

(¡UPDATE!: debería haberme leído con calma la página 64 del QL Technical Guide, que dice esto mismo que voy a decir yo ahora, bien clarito. En finx...)Algo expliqué antes, pero para simplificar: existe una señal en el interior del QL que permite desactivar a voluntad las dos ULA's, a la manera en que se hace en el Spectrum 48K. ¿Y por qué hace falta desactivar las ULA's cuando accedemos a la ampliación de memoria? Pues porque éstas son las responsables de direccionar y activar los primeros 256K del mapa de memoria: esto incluye la ROM del sistema, la ROM auxiliar, el espacio para periféricos del sistema, y los primeros 128K de RAM, y "gracias" a que la decodificación del bus de direcciones es incompleta, resulta que si no se desactivan las ULA's, al acceder a una dirección de memoria donde se supone que no hay nada, lo que tenemos es un "espejo" de los primeros 256K del mapa de memoria.

Por ejemplo: si en un QL original, sin expandir, hacemos un PEEK a la dirección 262144, lo que se lee es lo mismo que se leería en la dirección 0.

El resultado final de esto es que con la ampliación puesta, si no se desactivan la ULA's lo que pasará es que la memoria de la ampliación colisionará con lo que quiera que esté enviando el QL por la ROM o la RAM del sistema, según la dirección a la que accedamos (en el ejemplo del PEEK 262144 sería el primer byte de la ROM del sistema).

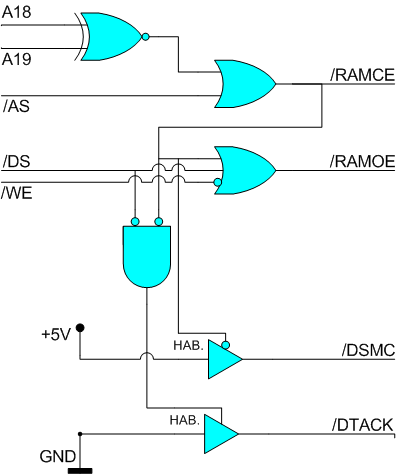

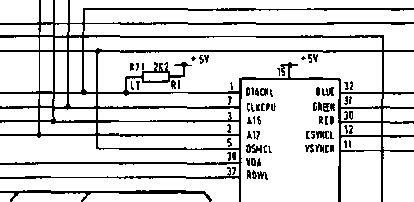

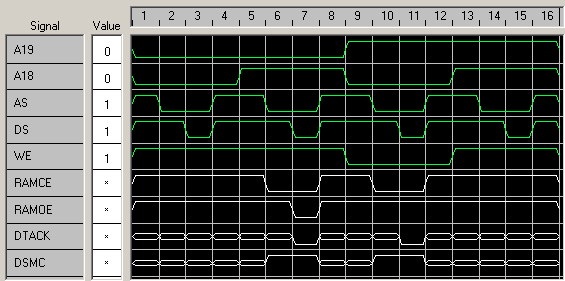

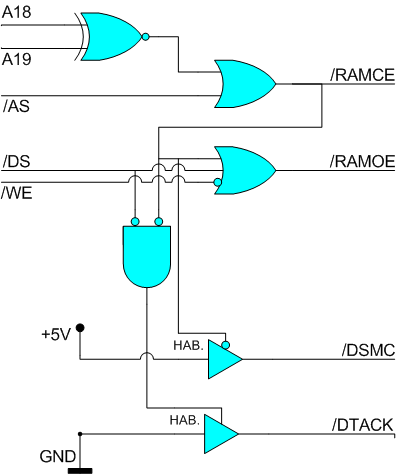

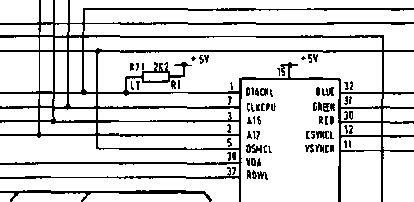

En el QL la señal que desactiva las ULA's se llama DSMC(L). En los esquemáticos y en otros documentos le ponen la L para indicar que es activa a nivel bajo. Yo simplemente la llamaré DSMC (Data Strobe Master Chip). Está en el pin 5 de IC22, entre otros lugares, y se muestra parcialmente en este esquema.

DSMC es una señal que, en principio, viene "casi" directamente desde la señal DS del procesador. Esta señal indica cuándo la transferencia de datos es posible desde o hacia el 68008. Si nunca baja, el dispositivo piensa que la CPU no está haciendo un ciclo de bus, y por tanto no hace nada. El "casi" de antes significa que DSMC está desacoplada de DS mediante una resistencia de 330 ohmios. Si nadie fuerza un valor 1 ó 0 en DSMC, esta señal seguirá las variaciones de DS, pero si un dispositivo externo fuerza un 1 en esta línea, DSMC dejará de seguir a DS y se quedará con el valor que le digamos.

En el QL hay dos formas de forzar esta línea a 1. La primera forma es bajando la señal VPA y a la vez, acceder a una dirección que tenga A18 ó A19 a 1. En la ampliación se cumple que la memoria se selecciona precisamente con esta combinación de A18 y A19, pero no bajamos VPA porque la memoria no es un periférico síncrono de la familia 6800 (que es para lo que sirve esta señal VPA) así que este método no nos vale.

EDITO: en realidad sí que vale. Lo acabo de comprobar  Si se hace así, basta con llevar la señal RAMCE directamente a VPA, con lo que la señal DSMC no hace falta ser generada.

Si se hace así, basta con llevar la señal RAMCE directamente a VPA, con lo que la señal DSMC no hace falta ser generada.La segunda forma es forzando directamente el 1 en la línea DSMC. Esto es lo que haremos nosotros. Para ello se ha añadido una ecuación más a la GAL que calcula el valor que debe tener DSMC para el ciclo de bus actual, y que puede ser "alta impedancia" o 1.

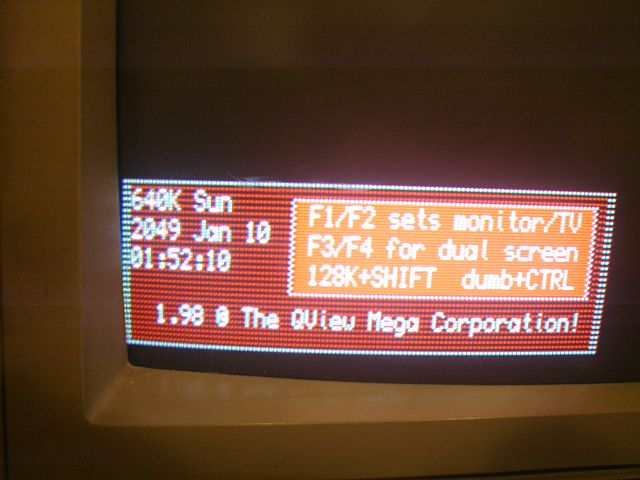

Y ahora sí que podemos arrancar el QL, y ver los resultados

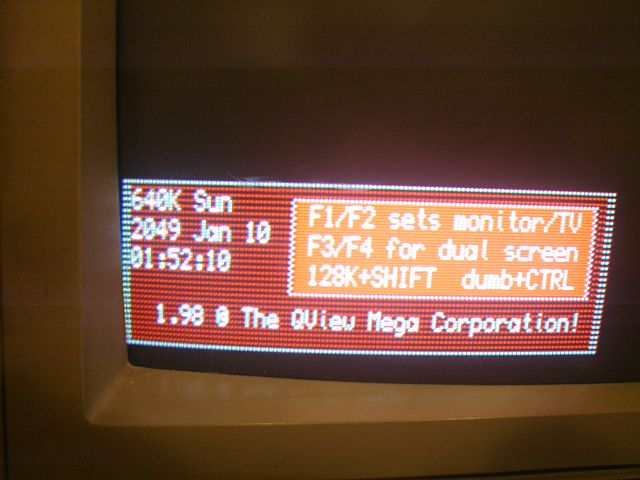

Se nota para empezar que tarda más en arrancar, debido a que se chequea mucha más memoria. Pero al final, obtenemos esto (arrancando con Minerva 1.98):

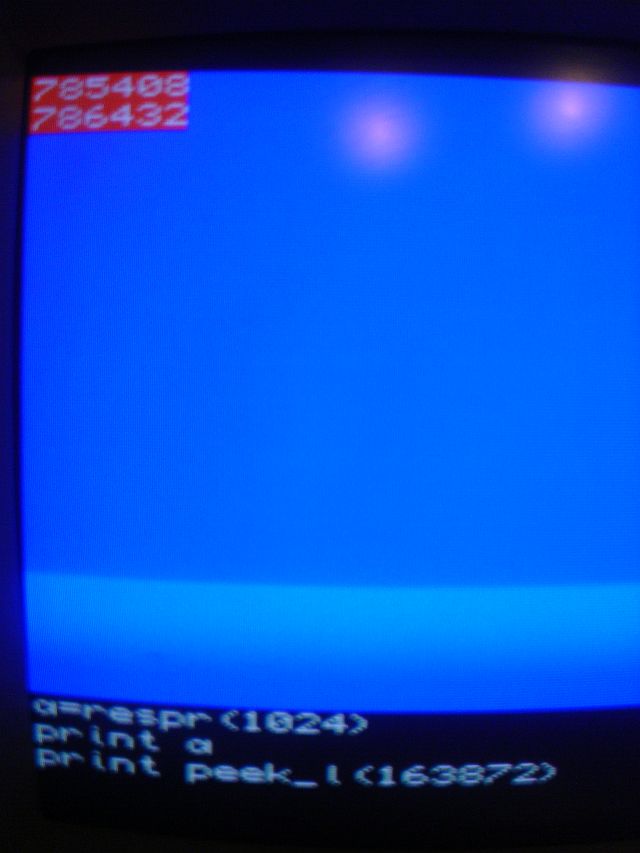

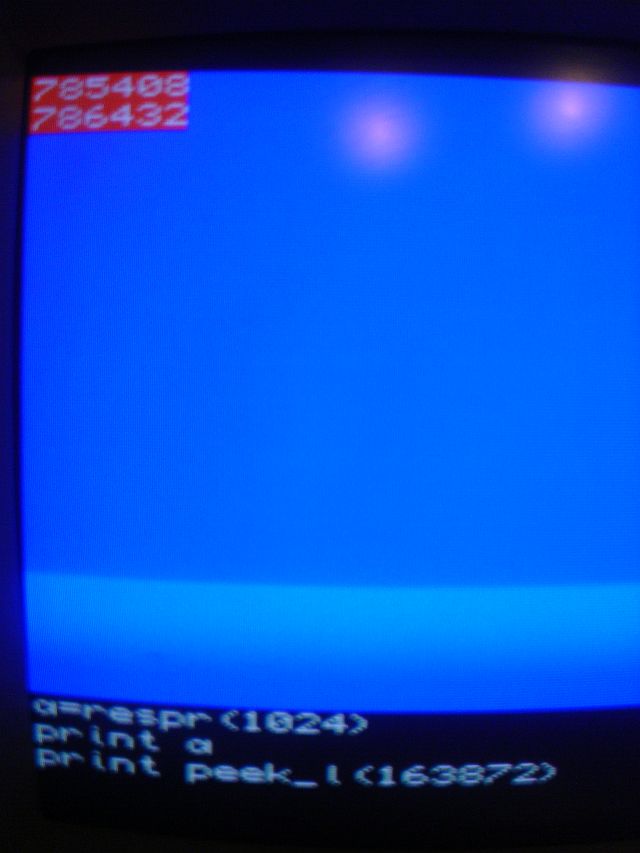

Y desde SuperBASIC, probando algunos comandos para ver dónde reserva memoria un RESPR, y usando una de las variables del sistema (una variable análoga a la variable P_RAMT del Spectrum) para obtener la dirección máxima de RAM+1 disponible:

El valor, 786432, corresponde en hexadecimal a C0000, que es ni más ni menos que el tope asignado a la memoria expandida del QL en el mapa de memoria

. En resumen: tenemos toda la RAM que oficialmente podemos tener en el QL

Por último, en lugar de poner las ecuaciones de la GAL, pongo el circuito equivalente que habría que hacer con componentes discretos. Si uno echa las cuentas, verá que necesitará un puñado de chips para implementar este circuito, por otra parte sencillo. Teniendo disponible las GAL, no hay color