Estos de ahora son cajas pequeñas que por USB se conectan al PC, y desde él se manejan. Todas las señales, etc. se visualizan en la propia pantalla del PC.

He hecho una prueba, analizando parte de las señales de un Spectrum, en concreto, uno que estoy arreglando para Metalbrain. He puesto puntas de prueba en el bus de datos, y en las señales CLK, MREQ, RD e INT.

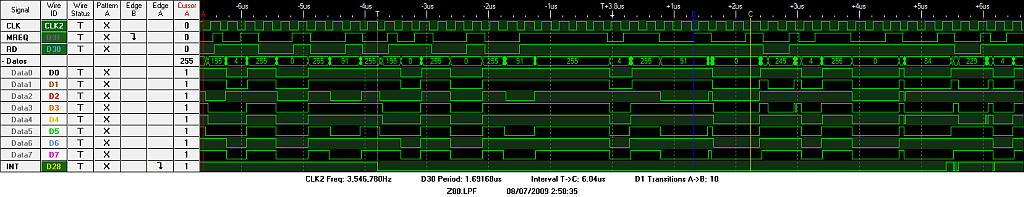

La prueba consiste concretamente en pedirle al analizador que comience a capturar datos en cuanto la señal INT pase de nivel alto a nivel bajo, es decir, en el momento en que la ULA dispare una interrupción enmascarable. En pantalla he agrupado los bits D0-D7 para que muestre su valor en decimal. Me interesa el valor cuando MREQ y RD pasan ambos de nivel bajo a nivel alto. Ese es el momento en que la CPU lee el dato que hay en el bus.

También veremos que hay momentos en que se escribe a memoria, aunque no he puesto la señal WR (mea culpa). Podremos, hasta cierto punto, discernir cuando es una lectura de una escritura porque en ésta última, RD se mantiene a nivel alto. Hay ocasiones no obstante, en que MREQ cambia de valor, RD está a nivel alto, y sin embargo no hay ninguna escritura. Esto pasa por ejemplo en los ciclos de refresco, que se suceden justo después de leer el código de operación de una instrucción.

Para obtener resultados predecibles, le he metido una rutinita consistente en:

Código: Seleccionar todo

ORG 23296

JP 23296Que se traduce en código máquina a: 195,0,91. Estos tres bytes es todo lo que ejecuta mientras no ocurra una interrupción.

Este ha sido el resultado (clic para ampliar):

En la parte de abajo de la figura se puede ver lo que ha tardado el procesador desde que saltó la interrupción hasta que comenzó a ejecutar la primera instrucción: 6,04 microsegundos. También podemos leer la frecuencia en la señal CLK2, que está conectada al CLK del procesador: 3,546 MHz .

El analizador lógico permite colocar cursores, que son simplemente marcas verticales de un color determinado, para poder señalar instantes determinados en el tiempo. Uno de ellos, el cursor T, se posiciona en el momento en que comenzó la captura de datos, es decir, cuando se dispara la interrupción. Se puede observar que ésta pilló al procesador en el segundo ciclo de la instrucción JP 23296, así que la interrupción tuvo que esperar a que finalizara (un ciclo después de leer el 91). En ese momento comienza el ciclo de aceptación de interrupción, en donde se ve cómo almacena en memoria (MREQ cae a nivel bajo pero RD queda a nivel alto, con lo que está escribiendo y no leyendo) los valores 91 y 0, en este orden. Ahí lo que está haciendo es almacenar en pila la dirección de retorno, y dado que la pila crece hacia abajo, lo almacena de tal forma que el LSB queda en la dirección más baja, así que la dirección que almacena es 0+256*91 = 23296, precisamente la dirección de retorno a la que debe saltar el procesador cuando termine la interrupción.

El cursor C está situado en el comienzo del primer ciclo de búsqueda de instrucción de la rutina de interrupción. En este ciclo se lee de memoria el código de operación de la primera instrucción de la rutina de interrupciones estándar de la ROM, que comienza en la dirección 56 decimal, o 38h hexadecimal. Si haceis PRINT PEEK 56 vereis cuál es ese código: el 245. En la figura, la lectura de memoria que se hace dos ciclos a continuación de la posición de C da el número 245. Es el código de PUSH AF.

Después de leer el 245 se ve que hace dos accesos a memoria pero no de lectura, sino de escritura: primero guarda el 0 y después el 84. Así que esos deben de ser los valores de A y F.

El siguiente acceso a lectura de memoria obtiene el valor 229. Ese es precisamente el número almacenado en la siguiente posición de la ROM: PRINT PEEK 57. Corresponde a PUSH HL.

Bueno, esto es lo que pasa cuando un Spectrum está "sano", o como en este caso, cuando se arranca con una ROM modificada para que no use la memoria superior (que es el síntoma que ofrece este Spectrum). ¿Qué pasa cuando lo enchufamos tal cual? ¿Ejecuta algo?

Este es el Spectrum, sin cartucho ROM de test, encendido. El aspecto es muy similar a cualquier otro Spectrum "estropeado" que hayáis podido ver, y que muchos dan por perdidos.

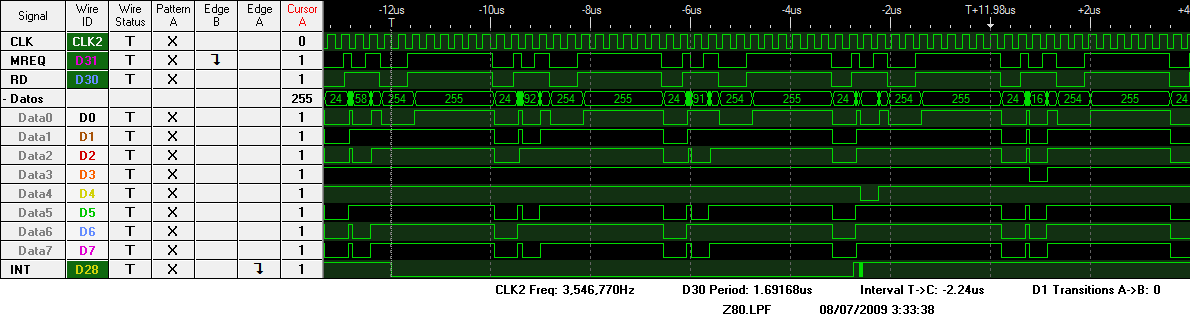

Y esta es la captura del analizador, tomada en el momento en que la ULA dispara una interrupción:

Como se ve, el Spectrum no está mirando a las musarañas, ni está completamente muerto. Se ve un patrón de bytes que se repite: 24,254,24,254,24,254. Al parecer la interrupción no ha hecho que se ejecute la rutina de interrupción, como en el caso anterior. Significa que cuando se ejecuta este código, lo hace con las interrupciones deshabilitadas. En algún punto anterior a éste, se ejecutó un DI, o bien este bucle se ejecutó poco después de arrancar la máquina, cuando aún no se habían habilitado las interrupciones (el Z80 arranca con las interrupciones deshabilitadas).

Mirando el código de operación 24, vemos que corresponde a JR disp. En este caso disp es 254, que en complemento a 2 es -1, así que esto es:

Código: Seleccionar todo

JR -1O puesto con etiquetas:

Código: Seleccionar todo

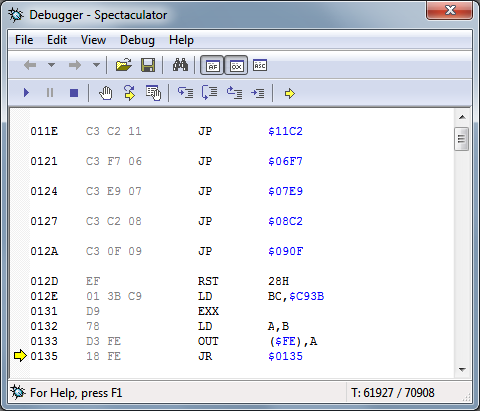

bucle: JR bucleEs decir, un bucle sin fin con las interrupciones deshabilitadas. Podría haber puesto más puntas lógicas para averiguar en qué dirección de memoria se está leyendo esa instrucción en la ROM, pero por vagueza no lo he hecho. En lugar de ello, he traceado la ROM en un emulador, hasta encontrar el punto donde se llama a la parte de la ROM que contiene el bucle infinito. Ese salto se produce durante el testeo de memoria, aquí:

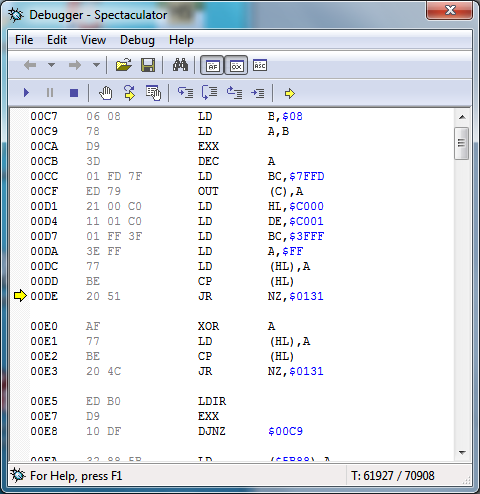

Se mete FF en una posición de memoria y acto seguido se comprueba si sigue allí. Si no, hay fallo de lectura y se salta a 0131.

Un poco más abajo se repite el test pero para el valor complementario, el 00. Si hay error se salta al mismo sitio.

Esta es la rutina donde todo finaliza. Se recupera el valor de B que indica qué banco de memoria es el que se está probando, y se pone el borde del color indicado en B. En la foto que he adjuntado el color es negro, lo que significa que el banco 0 falla. Hecho esto, se llega a un bucle sin fin, que es lo que hemos visto en el analizador.